Difference between revisions of "BoSL Board v0.5"

| Line 97: | Line 97: | ||

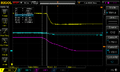

File:BoSLv0.5 Q1 oscilations edge.png| Fall edge of reset oscilations. Note that the drop in VREF causes Q1 gate voltage decrease, turning no Q1 which causes a rapid drop in +VBATT, further decreasing VREF. Yellow: +VBATT. Blue: VREF. Pink: Q1 gate voltage. | File:BoSLv0.5 Q1 oscilations edge.png| Fall edge of reset oscilations. Note that the drop in VREF causes Q1 gate voltage decrease, turning no Q1 which causes a rapid drop in +VBATT, further decreasing VREF. Yellow: +VBATT. Blue: VREF. Pink: Q1 gate voltage. | ||

</gallery> | </gallery> | ||

| + | |||

| + | To resolve this issue there are a number of things to try. The first of which is adding decoupling capacitors. First: one to VREF and one to +VBATT. | ||

Revision as of 04:15, 9 February 2024

Contents

2023 September 28

The BoSL board rev 0.5.0 arrived and its time to test how it works. Lets jump into it!

Straight out of the packet:

- Plugging in a battery the idle current 840 µA.

- Touching a screw driver to the F1 TEST pad lights up the test LED.

- When the WDT_EN jumper is closed the current jumps up to ~10 mA. This seems appropriate, if it enables the voltage on VPP.

From now on WDT_EN will be closed

- Voltage is good on 3V3 and VBAT. Measured (3.370V and 3.941V respectively).

- The bootloader could be programmed using the normal process of Arduino as ISP. Specifically I used the [[1]] board library and selected the ATmega640 board. I then used BOD: 2.7V, bootloader: yes UART0, clock: external 8MHz, EEPROM: EEPROM retain, compiler LTO: LTO disabled, pinout: AVR pinout.

- Idle current now 18 mA.

- I then plugged in the board via USB and it was recognised as a serial port.

- Programs could be uploaded via USB now, the serial monitor analogue read, and the RX,TX, LED, and USB, LEDs work.

- I could get a response form the SIM7000 when I made the following changes to the BoSLpass script.

- Replaced simCom soft serial object with Serial1

- set PWRKEY 38, DTR 44, and defined SIM_BUF_EN 25

- Pulled SIM_BUF_EN HIGH to turn on the voltage level converter.

- When I did this I could talk to the sim and recognise the simcard, but not register to the network. I suspect this is due to no Telstra reception here:

23:14:41.086 -> sending: AT+COPS=? 23:14:41.130 -> 23:37:12.814 -> 23:37:12.814 -> +COPS: (1,"vodafone AU","voda AU","50503",9),(1,"Optus AU","Optus","50502",9),,(0,1,2,3,4)

Firmware updates:

- Now that we have the more pins it would we wise to wrap each call which writes to the serial of the SIM7000 to first check CTS and RTS and see that we are allowed to send.

Errors:

- WDT_EN is not the correct name for the jumper as the WDT is disabled when closed. It should be not WDT_EN

- Add silkscreen for female pin headers

- Fix the pinout for U8, the MCP1700T-3302E which currently has the VPP and 3V3 swapped.

2023 November 26

Today I am testing the idle current draw of the BoSL board. First is to test the idle current when Q1 shuts off +BATT from VPP. All tests here are with WDT_EN open.

I swapped the orientation of U8 (MCP1700T-3302E) as it was incorrect. Doing this resulted in the idle current from 1.1 mA to 0.87 mA.

I do not notice any "floating rails" however if WDT_EN is enabled and then disabled it will take a long time for the VPP rail to return to 0V as the connected capacitors need time to discharge.

Removing the Zener diode for reverse current protection (D10) results in a current of 0.64 mA or a drop of approximately 200 μA.

The voltage measured on PB2 of the ATtiny4 (U7) is just indistinguishable from 0V, I do not think that the current leaking through the ATtiny to the ATmega via the WDT_KICK signal is a cause for the excessive current draw.

One the ATtiny (U7) was removed the idle current dropped to 2.7 μA, essentially zero. From this I conclude that the Zener diode D1 and the ATtiny U7 were using the majority of the current when WDT_EN is left open. Part of the reason the ATtiny was consuming ~600 μA of current is that it was not yet programmed. Programming the ATtiny will be a key next step in fixing the high power off current draw while still being able to use the ATtiny as a WDT.

Again with WDT_EN open VPP and 3V3 may appear floating however this is because there is residual charge in the capacitors which takes a long time to deplete.

WDT_EN closed sleep current

Here I will not investigate the smallest sleep current possible when WDT_EN is closed, that is when VPP and 3V3 have power.

Running a simple script which only has sleepMode(SLEEP_POWER_DOWN); sleep(); The total current draw of the board falls to 360 μA.

On U1, IN == VBAT and EN == 0V, so I do not believe that current is leaking through this pathway.

Despite the claimed 80 μA leakage of C1 (UWT1E331MNL1GS) in practice removing this capacitor had no discernible effect on the 360 μA idle current.

With D8,9,11 removed the idle current dropped to 180 μA. These diodes are used for connecting the SIM_PWRKEY and SIM_RESET between the SIM7000 and ATmega. (edit: maybe not)

2023 November 27

Programming the ATtiny4

To program the ATtiny4 I notice that PB0 (TPI_DATA) is also connected to the comparator and so will turn the board on and off whenever the data line is toggled. To prevent this I will cut the connection between R10 and C9 permanently keeping the board in the off state (no longer needed on >= v0.5.1). It is also necessary to ensure that WDT_DIS is not connected as this also will hold PB0 high. As a workaround you can hold the input to the MOFSET Q1 high while programming. The easiest way to do this is to connect the right pin on the WDT_DIS header to bottom right pin of Q1 (see image).

From the data sheet is appears that by default the reset pin is disabled and so a 12V signal must be applied to enable programming. This is correct once I used a 12V reset signal I could program the ATtiny4 using [[2]] this Arduino Uno script, a few resistors and jumper wires. This script can also be used to reenable the reset pin so 12V is no longer needed.

With the following program uploaded (given in as a hex file) the current of the BoSL v0.5 dropped to just 2.7 µA. This file puts the ATtiny into deep sleep mode.

:1000000009C010C00FC00EC00DC00CC00BC00AC08C :1000100009C008C011271FBFCFE5D0E0DEBFCDBFAC :1000200002D00DC0EDCF4AB7417F44604ABF4AB706 :1000300041604ABF88954AB74E7F4ABFFFCFF894C8 :02004000FFCFF0 :00000001FF

On the BoSL v0.5.2 is it not possible to program the ATtiny4 without hardware modification as PB0 (DATA) toggles the mosfet power switch (Q1) on and off which causes large voltage spikes on +BATT. A workaround for this is to hold the MOSFET gate high. I think going forward a possible hardware solution is to move the JP1 (WDT_DIS) jumper to pull the mosfet high rather than before the comparator. With this strategy it may also be good buffer the output of the comparator with a resistor to minimise extraneous current draw. This will need some investigation.

2024 February 1

With the above code which disables the ATtiny, on the BoSL v0.5.2 we can now get a Q1 off current of 2.7 µA, and a ATmega640 sleep current of 120 µA.

2024 February 09

Today I discovered, an issue with the undervoltage protection on the BoSL v0.5.2. At voltages near the cut off ~ 3.6 V a dangerous oscillation occurs in the switch-comparator system. As part of this oscillation the power MOSFET Q1 will rapidly turn on and off at a rate of ~ 300 Hz, this causes a ripple of about 700 mV on VPP. This is the rail which all components on the BoSL v0.5 other than the reset circuitry.

To resolve this issue there are a number of things to try. The first of which is adding decoupling capacitors. First: one to VREF and one to +VBATT.